2020年7月14日,JEDEC宣布发布JESD79-5 DDR5 SDRAM标准,这标志着行业即将向DDR5服务器双列直插式内存模块(DIMM)过渡。DDR5内存为台式机带来了许多关键的性能和功率增益,以及新的设计挑战。服务器系统架构师,设计人员和购买者都想知道DDR5 vs DDR4的新功能,以及如何从新一代内存中获得最大收益。

DDR5 vs DDR4有什么变化?

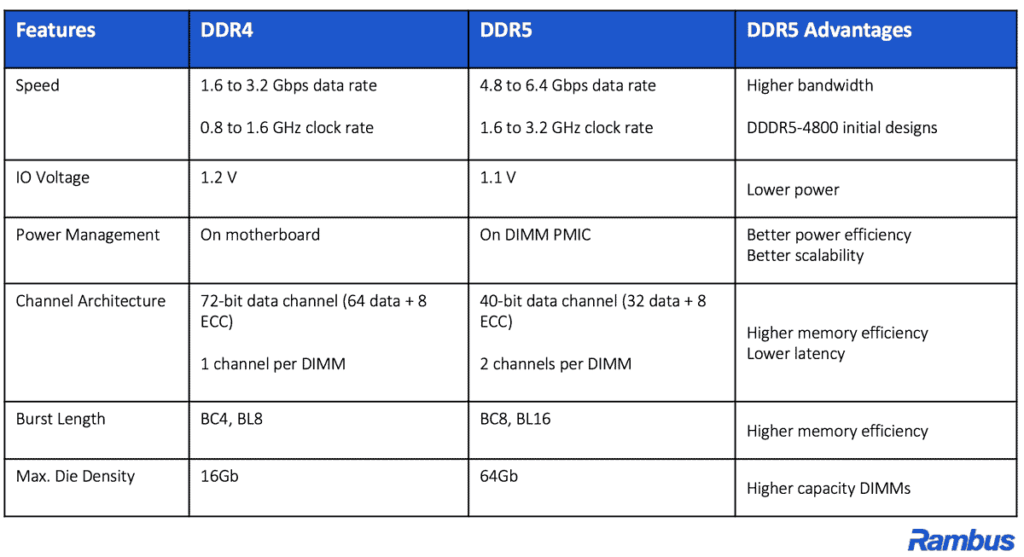

下表1显示了从DDR4到DDR5 DIMM的过渡中最重要的六项最重要的规格改进。

表1. DDR5与DDR4:DDR5相对于DDR4 DIMM的优势

1. DDR5扩展到6.4 Gbps

您永远无法拥有足够的内存带宽,而DDR5可以满足不断增长的速度需求。DDR4 DIMM的最高时钟频率为1.6千兆赫兹(GHz)时达到每秒3.2吉比特(Gbps),而最初的DDR5将使带宽增加50%,达到4.8 Gbps。DDR5内存最终将使DDR4 DRAM的数据速率翻一番,达到6.4 Gbps。DDR5中集成了决策反馈均衡(DFE)等新功能,从而实现了更高的IO速度。

2.较低的电压意味着较低的功率

第二个主要变化是工作电压(VDD)的降低,这将转化为更低的功率。使用DDR5时,DRAM和缓冲芯片注册时钟驱动器(RCD)电压从1.2 V下降至1.1V。但是,较低的VDD意味着较小的抗扰度裕度,设计人员必须对其实施加以认识。

3. DDR5的新电源架构

第三个也是主要的变化是电源体系结构。对于DDR5 DIMM,电源管理从主板转移到DIMM本身。DDR5 DIMM在DIMM上将具有12V电源管理IC(PMIC),以实现更好的系统电源负载粒度。PMIC分配1.1 V VDD电源,通过对电源进行更好的On-DIMM控制来帮助实现信号完整性和噪声。

4. DDR5与DDR4通道架构

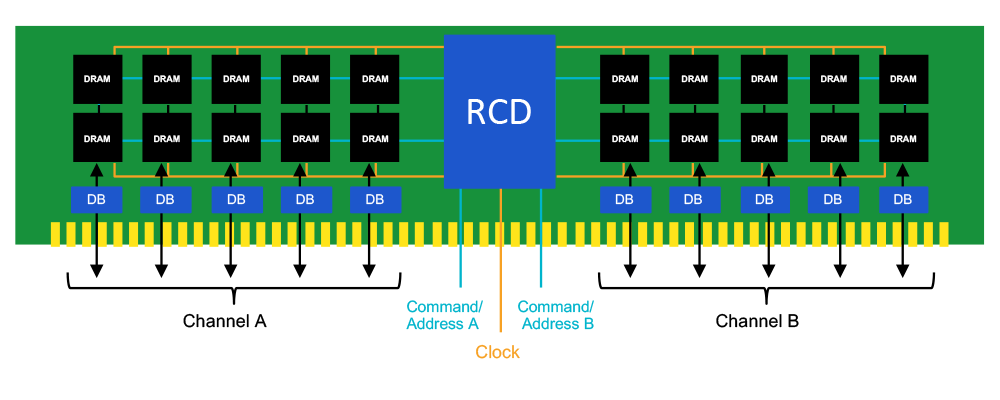

DDR5的另一个重大变化是新的DIMM通道架构,在我们的榜单上排名第四。DDR4 DIMM具有72位总线,包括64个数据位和8个ECC位。使用DDR5,每个DIMM将具有两个通道。这些通道中的每个通道均为40位宽:32个数据位和8个ECC位。尽管数据宽度相同(总共64位),但具有两个较小的独立通道可提高内存访问效率。因此,您不仅可以受益于DDR5带来的速度提升优势,而且更高的MT / s优势也可以通过更高的效率得到放大。

在DDR5 DIMM体系结构中,DIMM的左侧和右侧分别由一个独立的40位宽通道提供服务,它们共享RCD。在DDR4中,RCD每侧提供两个输出时钟。在DDR5中,RCD每侧提供四个输出时钟。每个40位通道的32位数据由四个8位通道组成,这些通道中的每个通道都从RCD获取独立的时钟信号。为每个通道提供独立的时钟可改善信号完整性,从而有助于解决由于降低VDD而产生的噪声容限较低的问题(来自上述更改2)。

5.更长的爆发长度

第五个主要变化是突发长度。DDR4突发斩波长度为4,突发长度为8。对于DDR5,突发斩波和突发长度将扩展到八和十六,以增加突发有效负载。突发长度为十六(BL16),允许单个突发访问64字节的数据,这是典型的CPU缓存行大小。它只能使用两个独立通道之一来执行此操作。这显着提高了并发性,并通过两个通道提高了内存效率。

6. DDR5支持更高容量的DRAM

DDR5的第六个也是最后一个更改是对更高容量的DRAM设备的支持。借助DDR5缓冲芯片DIMM,服务器或系统设计人员可以在单个管芯封装中使用多达64 Gb DRAM的密度。DDR4在单芯片封装中最大可容纳16 Gb DRAM。DDR5支持诸如片上ECC,错误透明模式,封装后修复以及读和写CRC模式等功能,以支持更大容量的DRAM。

DDR5设计面临哪些挑战?

DDR5的这些变化引入了许多设计问题,涉及更高的速度和更低的电压-提出了新一轮的信号完整性挑战。设计人员将需要确保母板和DIMM能够处理更高的信号速度。在执行系统级仿真时,需要检查所有DRAM位置的信号完整性。

对于DDR4设计,主要的信号完整性挑战在于双数据速率DQ总线,而对低速命令地址(CA)总线的关注较少。对于DDR5设计,即使CA总线也需要特别注意以确保信号完整性。在DDR4中,考虑使用差分反馈均衡(DFE)来改善DQ数据通道。但是对于DDR5,RCD的CA总线接收器还将需要DFE选项,以确保良好的信号接收。

主板上的供电网络(PDN)是另一个考虑因素,包括带PMIC的DIMM。考虑到更高的时钟和数据速率,您将需要确保PDN能够以更高的速度,良好的信号完整性以及为DIMM提供良好的清洁电源来处理运行负载。

从主板到DIMM的DIMM连接器也必须处理新的时钟和数据速率。对于系统设计人员而言,在印刷电路板(PCB)周围具有较高的时钟速度和数据速率的情况下,必须更加着重于系统设计,以实现电磁干扰和兼容性(EMI和EMC)。

DDR5内存接口芯片组如何利用DDR5的DIMM优势?

好消息是,DDR5内存接口芯片改善了从主机内存控制器发送到DIMM的命令和地址信号的信号完整性。两个通道中的每个通道的总线都通向RCD,然后呈扇形散开到DIMM的两半。RCD有效地减少了主机内存控制器看到的CA总线上的负载。

DDR5数据缓冲芯片将减少数据总线上的有效负载,从而在不降低延迟的情况下在DIMM上启用更高容量的DRAM。